Runsheng Wang

Peking University, China

dram

random telegraph noise

tem

monte carlo

cryogenics

finfet

aging

leakage

nbti

tddb

hot carrier degradation

data retention time

interface trap

oxide trap

finfets

8

presentations

8

number of views

SHORT BIO

Runsheng Wang received the B.S. and Ph.D. (highest honors) degrees from Peking University, Beijing, China, in 2005 and 2010, respectively. From November 2008 to August 2009, he was a Visiting Scholar with Purdue University, West Lafayette, IN, USA. He joined Peking University in 2010, where he is currently an Associate Professor at the Institute of Microelectronics. He has authored/coauthored 1 book, 3 book chapters, and over 100 scientific papers, including more than 30 papers published in International Electron Devices Meeting (IEDM) and Symposium on VLSI Technology (VLSI-T). He has been granted 12 US patents and 29 Chinese patents. His current research interests include nanoscale CMOS devices, characterization and reliability, design-technology co-optimization (DTCO) and EDA, emerging technologies and circuits for new-paradigm computing. Dr. Wang was awarded the IEEE EDS Early Career Award by the IEEE Electron Device Society (EDS), NSFC Award for Excellent Young Scientists by the National Natural Science Foundation of China (NSFC), Natural Science Award (First Prize) by the Ministry of Education (MOE) of China, and many other awards. He serves on the Editorial Board of IEEE TRANSACTIONS ON ELECTRON DEVICES, Scientific Reports, and SCIENCE CHINA: Information Sciences, and has served on the Technical Program Committee of many IEEE conferences, including IEDM, IRPS, EDTM, IPFA, etc.

Presentations

DRAM Technology under Negative Bias Temperature Instability (NBTI) : from Characterization to Physical Origin Identification

Da Wang and 9 other authors

Investigation of Positive Bias Temperature Instability in advanced FinFET nodes

Yongkang Xue and 9 other authors

Investigation of Interplays between Body Biasing and Hot Carrier Degradation (HCD) in Advanced NMOS FinFETs

Zixuan Sun and 7 other authors

Accelerating Device-Circuit Self-heating Simulations with Dynamic Time Evolution for GAAFET

Sihao Chen and 6 other authors

New Insights into the Random Telegraph Noise (RTN) in FinFETs at Cryogenic Temperature

Zirui Wang and 6 other authors

Towards the Characterization of Full ID-VG Degradation in Transistors for Future Analog Applications

Pengpeng Ren and 5 other authors

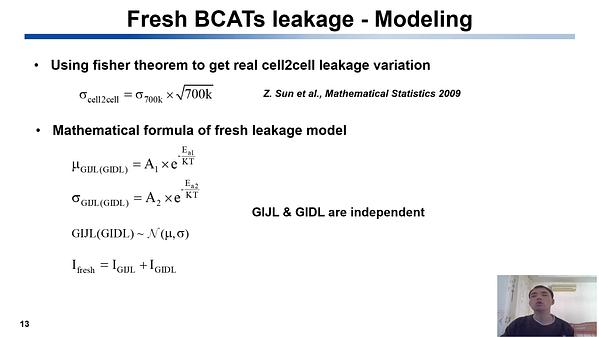

New Insight into the Aging Induced Retention Time Degradation of Advanced DRAM Technologies

Yong Liu and 7 other authors

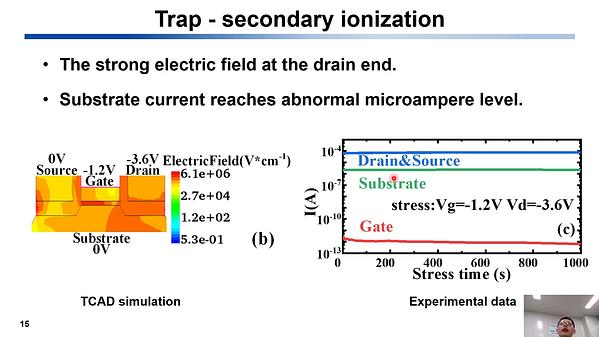

Characterization and Modelling of Hot Carrier Degradation in pFETs under Vd>Vg Condition for sub-20nm DRAM Technologies

Da Wang and 7 other authors