Javier Diaz Fortuny

imec, Belgium

integrated circuit reliability

tamper detection

bias temperature instabilities (bti)

ring-oscillator

hardware security

array chip

hot carrier injection (hci)

transistor array

hkmg

processor

cell libraries

off-state stress

nfets

tdv

puf

5

presentations

4

number of views

SHORT BIO

Javier Diaz Fortuny is currently working as a full-time researcher in the EFT (Electrical and Functional Testing) team within the AR2T (Advanced Reliability, Robustness & Testing) department at imec. His main research focus is the study of Time-Dependent Variability phenomena in ultrascaled CMOS technologies to create Hardware Security roots-of-trust.

Presentations

Statistical characterization of off-state stress degradation in planar HKMG nFETs using device arrays

Pablo Saraza-Canflanca and 6 other authors

Machine Learning Unleashes Aging and Self-Heating Effects: From Transistors to Full Processor

Hussam Amrouch and 3 other authors

Demonstration of Chip Overclock Detection by Employing Tamper-aware Odometer Technology

Javier Diaz Fortuny and 5 other authors

A Smart SRAM-Cell Array for the Experimental Study of Variability Phenomena in CMOS Technologies

Pablo Saraza-Canflanca and 6 other authors

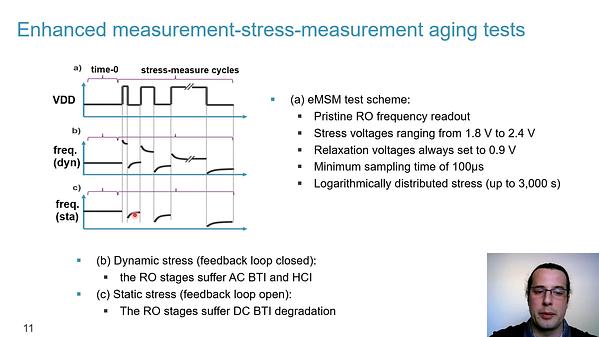

A Ring-Oscillator-based Degradation Monitor Concept with Tamper Detection Capability

Javier Diaz Fortuny and 4 other authors